差分情報記憶方式(DISS)不揮発レジスタ

従来レベルの短い時間動作で消費電力と面積を低減

概要

不安定なエネルギー供給下でも継続的な演算処理を可能にする間欠的コンピューティングのエッジデバイス実装において,不揮発記憶回路(不揮発レジスタ)を活用し、ローカルなデータ転送のみで内部状態を不揮発記憶処理できる不揮発ロジック回路構造が有望な選択肢となる。

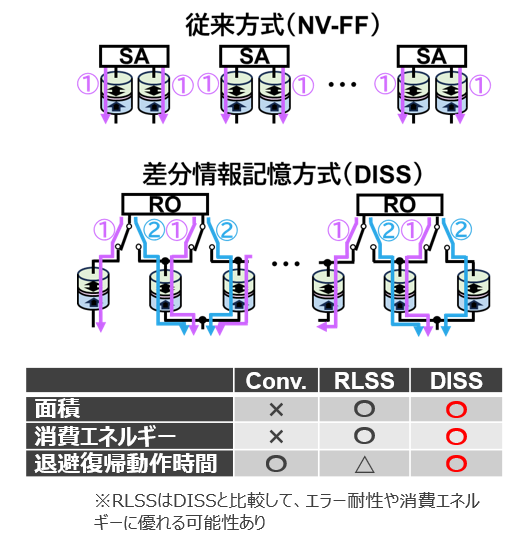

従来の不揮発レジスタは、1ビット記憶回路(不揮発フリップフロップ、NV-FF)をビット数分接続する構成であり、1ビットあたり2個のMTJ素子を必要とするため、面積やエネルギーのオーバーヘッドが大きいという課題があった。これに対して発明者らは共有リファレンス方式(RLSS)という処理により消費エネルギーおよび面積を低減する効果をシミュレーションで確認したが、動作に必要な時間はレジスタのビット数に比例して増加するという新たな課題が生じた。

本発明は差分情報記憶方式(DISS)という方式を提案する。具体的には1ビットのデータを隣り合う2つのMTJ素子の抵抗状態の差分によって保持することで、バックアップ・リストアがそれぞれ2サイクルの動作で可能となり、消費エネルギーおよび面積の低減に加えて、動作時間も従来方式並みに抑える効果をシミュレーションで確認した。

バックアップ・リストア動作および性能の比較

応用例

・不揮発レジスタ、不揮発フリップフロップ

・間欠的コンピューティング・エナジーハーべスティング

・既存のデスクトップやスーパーコンピュータの消費電力削減

関連文献

[1] DOI: 10.1109/MWSCAS60917.2024.10658712

知的財産データ

知財関連番号 : 特願2024-230132

発明者 : 夏井 雅典、吉田 知生、羽生 貴弘

技術キーワード: 不揮発レジスタ、 不揮発フリップフロップ、 間欠的コンピューティング、 エナジーハーべスティング、 消費電力削減